### Minimum and Maximum Mode

#### System and Timings

By,

Hitha Paulson Assistant Professor, Dept of Computer Science LF College, Guruvayoor

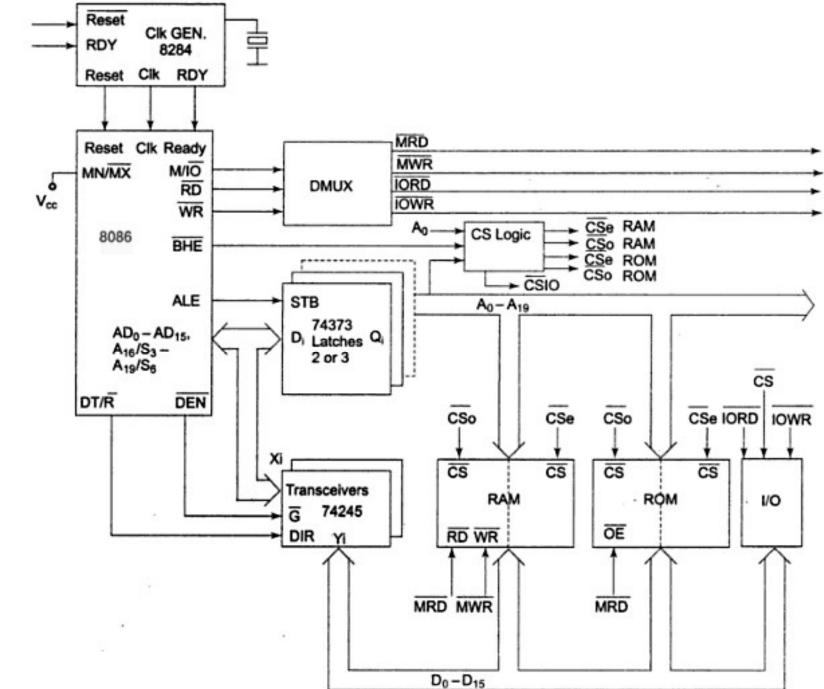

used for medium system to large system includes two or more processors.

|        |    |      |    | MODE MODE     |

|--------|----|------|----|---------------|

| GND C  | 1  |      | 40 | b vcc         |

| AD14   | 2  |      | 39 | AD15          |

| AD13 [ | 0  |      | 38 | A16/S3        |

| AD12   | 4  |      | 37 | A17/54        |

| AD11   | 5  |      | 36 | A18/55        |

| AD10   | 6  |      | 35 | A19/56        |

| AD9 C  | 1  |      | 34 | BHE/ST        |

| ADS [  | 8  | yele | 33 | MN/MX         |

| AD7 C  | 9  | -    | 32 | RD            |

| AD6    | 10 | CPU  | 31 | RO/GTO (HOLD) |

| AD5    | 11 |      | 30 | RO/GTT (HLDA) |

| AD4    | 12 |      | 29 | LOCK (WR)     |

| AD3    | 13 |      | 28 | 3 52 (M/IO)   |

| AD2    | 14 |      | 27 | 51 (DT/A)     |

| AD1    | 15 |      | 26 | 50 (DEN)      |

| ADO C  | 16 |      | 25 | OSO (ALE)     |

| NMI C  | 17 |      | 24 | OSI (INTA)    |

|        | 18 |      | 23 | TEST          |

| CLK [  | 19 |      | 22 | READY         |

| GND    | 20 |      | 21 | RESET         |

## Minimum Mode Pins

|                     |            |                   | the second |

|---------------------|------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                 | Symbol     | In/Oùt<br>3-State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                     | INTA       | 910-3<br>9101 101 | Indicates recognition of an interrupt request.<br>Consists of two negative going pulses in two<br>consecutive bus cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

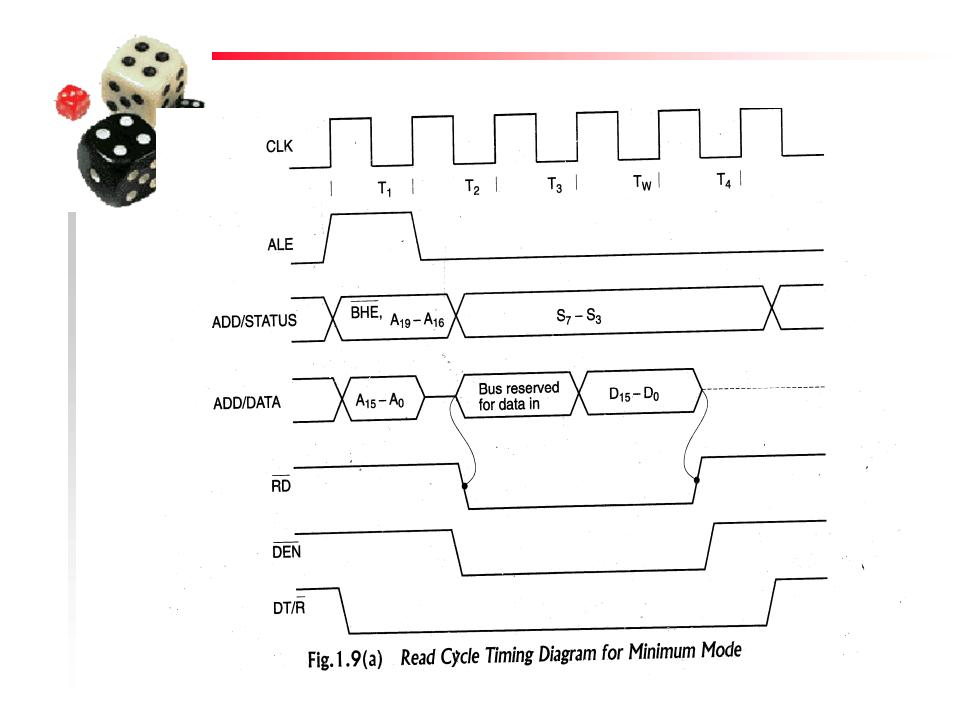

| 25                  | ALE        | 0                 | Outputs a pulse at the beginning of the bus cycle<br>and is to indicate an address is available on<br>the address pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 26                  | DEN        | 0-3               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 27                  | DT/R       | 0-3               | Indicates to the set of transceivers whether they are to transmit (1) or receive (0) data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 281                 | M/IO       | 0-3               | Distinguishes a memory transfer from an I/O<br>transfer. For a memory transfer it is 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     | WR<br>MR   | 0-3               | When 0, it indicates a write operation is being<br>performed. It is used in conjunction with pins<br>28 (M/IO) and 32 (RD) to specify the type of transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 30                  | HLDA       | 0                 | Outputs a bus grant to a requesting master. Pins<br>with tristate gates are put in high impedance<br>state while HLDA=1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 31                  |            | I                 | Receives bus requests from bus masters. The 8086/8088 will not gain control of the bus until this signal is dropped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <sup>1</sup> For th | e 8088, ti | ne symbol         | is $IO/\overline{M}$ and a 1 indicates an $I/O$ transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

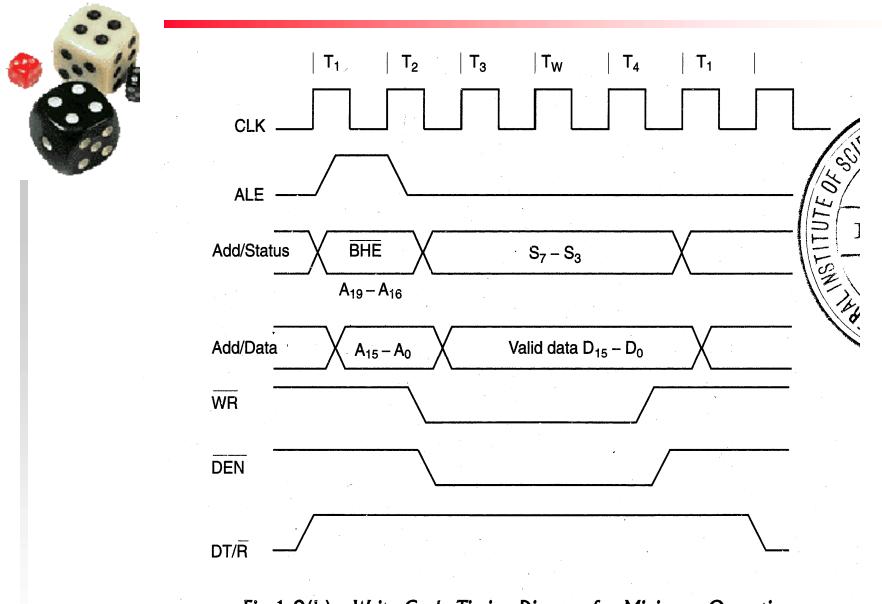

Fig. 1.9(b) Write Cycle Timing Diagram for Minimum Operation

#### Pin Symbol In/Out Description 3-State 24,25 QS1,QS0 0 Reflects the status of the instruction queue. This status indicates the activity in the queue during the previous clock cycle - see Chap. 11. 26,27,28 \$0,\$1,\$2 Indicates the type of transfer to take place 0-3 during the current bus cycle: S2 <u><u></u>S1</u> SO 0 0 Interrupt acknowledge 0 0 0 Read I/O port 0 0 Write I/O port Halt Instruction fetch 0 0 0 Read memory Write memory 0 Inactive - passive (1 represents high and 0 represents low.) The status becomes active prior to the beginning of a bus cycle and returns to inactive during the later part of the cycle. 29 LOCK 0-3 Indicates the bus is not to be relinquished to other potential bus masters. It is initiated by a LOCK instruction prefix and is maintained until the end of the next instruction - see Chap. 11. It is also active during and between the two INTA pulses. 30 RO/GT1 I/0 For inputting bus requests and outputting bus grants. 31 RQ/GTO I/0 Same as RO/GT1 except that a request on RQ/GTO has higher priority.

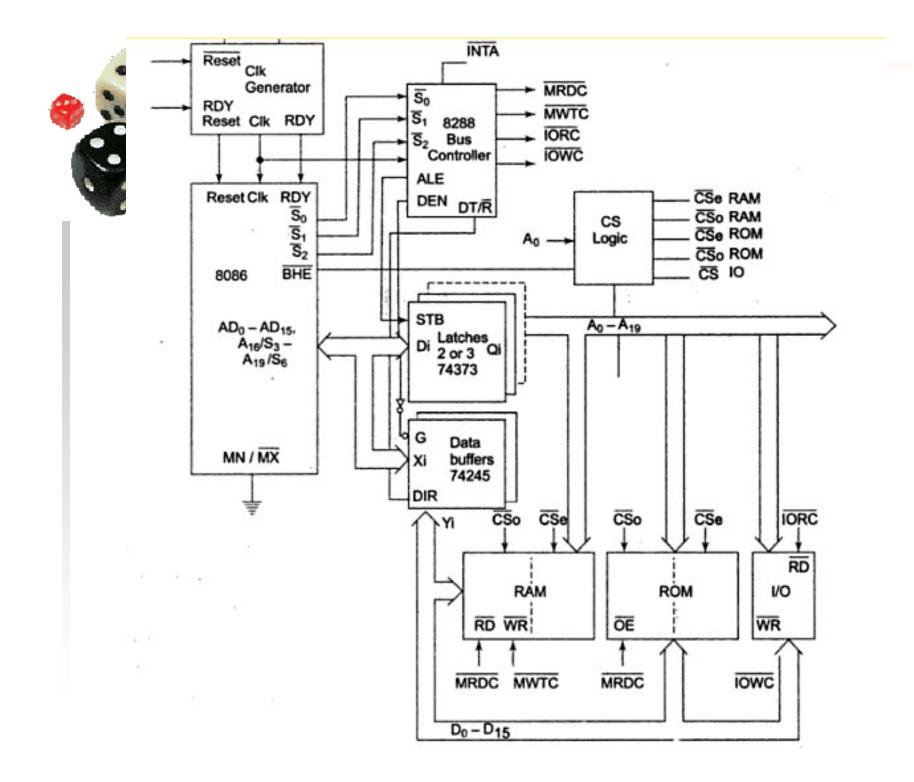

# Maximum Mode Pins